並列領域分割法による半導体デバイスシミュレーション

氏名:小田中紳二,鍾菁廣

所属:大阪大学サイバーメディアセンター

概要:新材料・新構造(3次元構造)を持つ半導体デバイスの特性解析のためには、半導体デバイスシミュレーションの高速化が重要である。本研究ではマルチコア・マルチノードアーキテクチャに適した並列計算モデルを考える。

ノード間並列はRestricted Additive Schwarz法に基づいた並列領域分割法を適用し、ノード内並列は分割作用素法による不完全分解の高速化を図ることでハイブリッドMPI/OpenMP並列計算モデルを構築した。

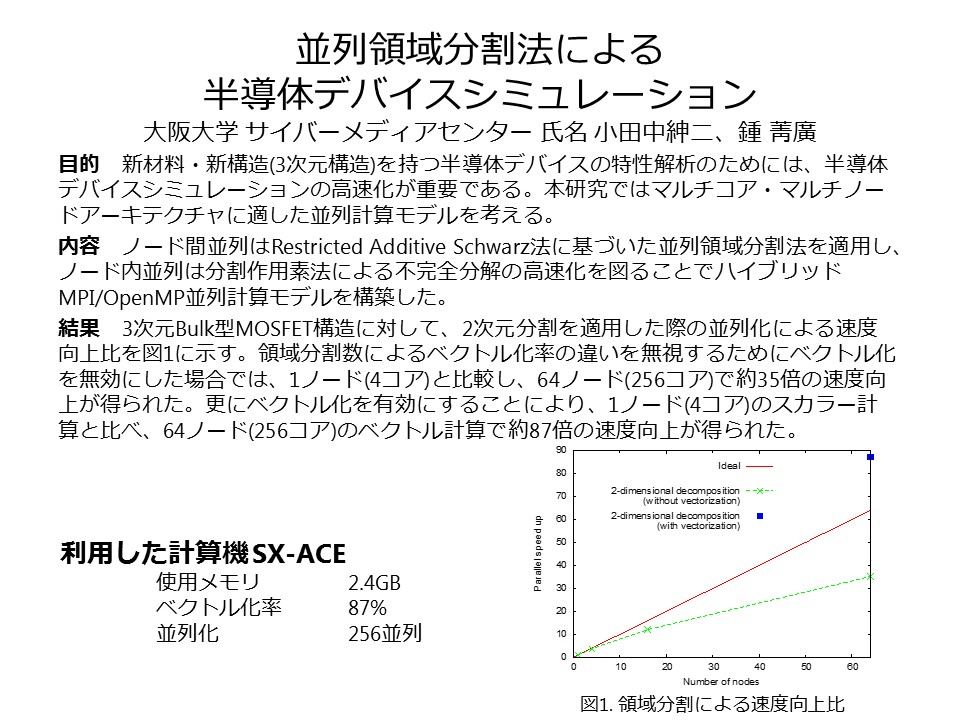

3次元Bulk型MOSFET構造に対して、2次元分割を適用した際の並列化効率を評価した。領域分割数によるベクトル化率の違いを無視するためにベクトル化を無効にした場合では、1ノード(4コア)と比較し、64ノード(256コア)で約35倍の速度向上が得られた。更にベクトル化を有効にすることにより、1ノード(4コア)のスカラー計算と比べ、64ノード(256コア)のベクトル計算で約87倍の速度向上が得られた。

論文掲載,発表実績:

(国際会議会議録掲載論文)

- Shohiro Sho, “A parallel semiconductor device simulation on SX-ACE”, NEC user group meeting, Osaka university , Japan, 2016

(国内研究会等発表論文)

- 鍾菁廣, 小田中紳二,“メニィコア時代の3次元ドリフト拡散モデルの並列化手法”, 応用物理学会 シリコンテクノロジー分科会 第193回 研究集会, pp. 31-35, July 2016.

Posted : 2017年03月30日